La arquitectura PowerPC, ahora incluida en la

denominación Power, es una de las mejores y más

extendidas implementaciones de procesadores RISC. A

diferencia de los computadores CISC, se caracterizan por

tener un juego de intrusiones más simple que permite

simplificar su diseño y una mayor cantidad de registros

para obtener un rendimiento superior. Ejemplos de estos

microprocesadores son el PowerPC 601, el primer

PowerPC de la historia, el PowerPC 7450, al que Apple

llamó G4 y el PowerPC 970 usado en supercomputadores

como el MareNostrum de Barcelona. Pero los PowerPC se

usan también en microcontroladores, automóviles e incluso

aviones, como el PowerPC 401. El futuro de los Power, se

centra en el Cell y el nuevo POWER6 de IBM.

Introducción

En este blog se van a introducir ideas básicas

que componen los pilares de la arquitectura PowerPC,

como es la filosofía de diseño de computadores RISC, en la

que se fundamenta la arquitectura. Además, se hará un

breve repaso a la evolución de la corta, pero intensa,

historia de esta arquitectura.

Filosofía de diseño y repertorio de instrucciones de

procesadores RISC.

Antes de la aparición de los procesadores RISC

(Reduced Instruction Set Computer), la filosofía de diseño

de los procesadores se basaba en aumentar la potencia de

proceso agregando mayor capacidad de almacenamiento en

forma de registros. Este hecho condujo a un problema y es

que los registros se implementan en los procesadores

usando transistores en el propio dado del procesador,

además de que incrementan en gran medida la complejidad

de las CPUs, pues todas sus unidades funcionales han de

estar “cableadas” con todos los registros. En este sentido, la

utilización de la memoria principal simplificaba el diseño y

lo abarataba, por lo que los microprocesadores limitan el

número de registros que implementan en su interior.

Para poder usar la memoria principal para almacenar la

información de las unidades funcionales de la CPU, se

intentó implementar las instrucciones de manera que

ofrecieran varias versiones en función de la posición de los

operandos de las mismas, ya sea en registros internos o

memoria principal, y simplificar la programación. Este

concepto se conoce como ortogonalidad. Hace que un

menor número de instrucciones permitan realizar las

mismas operaciones, pues la misma instrucción puede ser

configurada para diferentes modos de direccionamiento.

La ortogonalidad proporciona una mayor sencillez a la

hora de programar una CPU, pero complica su desarrollo.

Con el auge del uso de compiladores, el

direccionamiento ortogonal cae en desuso, pues no tienen

la suficiente “inteligencia” como para aprovechar todos los

modos de direccionamiento que una CPU ofrecía, por lo

que sólo los programas escritos en bajo nivel (ensamblador)

podían aprovecharla.

La filosofía RISC se basa en reducir los modos de

direccionamiento y la cantidad de operaciones que realiza

una instrucción manteniendo la continuidad del flujo de

instrucciones en el cauce segmentado y creando un juego

de instrucciones más simples y más pequeño que los juegos

de instrucciones de computadores CISC (Complex

Instruction Set Computer).

Las instrucciones más simples requieren un menor

número de pasos o ciclos para ejecutarse, aunque realicen

también menos operaciones, mientras que las instrucciones

complejas requieren un mayor número de pasos, pero

realizan más operaciones. Con esto, se puede decir que, en

general, un programa requerirá más cantidad de

instrucciones simples para hacer lo mismo que otro

programa con instrucciones complejas. Por esto, no es fácil

discernir cuál de las dos alternativas proporciona un mayor

rendimiento.

La clave viene con la implementación de sistemas con

segmentación del cauce de ejecución, pues es más simple

implementar cauces eficientes para conjuntos reducidos de

instrucciones [1]. En general, los cauces de ejecución de

procesadores RISC serán más cortos que los de

procesadores CISC, aunque no es algo que se pueda

considerar como regla general, pues el PowerPC 970 de

IBM tiene más etapas que el Core 2 Duo de Intel,

ofreciendo el segundo un mayor rendimiento medio

(throughput).

Breve reseña histórica de la arquitectura PowerPC.

La filosofía RISC fue introducida por John Cocke en los

años 70. La primera implementación de un procesador

RISC llegaría con el proyecto 801 de IBM, dedicado

especialmente a computación empotrada. Ofreció un

rendimiento bastante malo, por lo que IBM emprendió el

Proyecto América, creando el primer procesador de la

arquitectura POWER [3], incluido en el RISC System/6000

a principios de los 90.

En 1991, IBM se dio cuenta de las posibilidades de su

diseño y se creó la alianza AIM (Apple, IBM & Motorola,

actualmente Freescale), con el objetivo de terminar con el

domino del tándem Microsoft-Intel que ofrecía sistemas

basados en 80386 y 80486 y tenía al Pentium en desarrollo.

Para Motorola supuso una salida al poco éxito que estaba

teniendo su serie 88000, por lo que requirió que la nueva

solución fuera compatible con el bus del 88000 a nivel de

hardware.

El resultado de estos requerimientos fue la arquitectura

PowerPC (Performance Optimization With Enhanced RISC

Performance Computing).

La primera implementación de un procesador PowerPC

llegó en 1993 con el PowerPC 601 de IBM.

Los primeros productos tuvieron cierto éxito, Motorola

implementó sus propios sistemas y Microsoft portó

Windows NT 3.51 a la arquitectura. Aunque en la

actualidad sólo versiones de Linux y Mac OS X siguen

estando disponibles para PowerPC (Apple ha decido

utilizar procesadores Intel en sus líneas de productos, por lo

que sólo Linux quedará como SO de sobremesa para los

procesadores PowerPC).

Ejemplos de implementaciones de sobremesa fueron los

procesadores 750 (G3), 7400 (G4), 7450 (G4e) y sus

múltiples versiones (7447, 7447a y 7448) y el 970 (G5) y

sus derivaciones: 970FX, 970MP y 970GX.

Aplicaciones actuales de los procesadores PowerPC

Esta arquitectura ha tenido mucho éxito en entornos

empotrados, con representantes como el PowerPC 401 y

diversos microcontroladores desde 8 a 32 bits, usados en

automóviles, controladores de red e incluso aviones (el

nuevo Airbus A380, lleva 25 chips PowerPC y el SO de

tiempo real LynxOS).

Se han construido numerosos supercomputadores en

torno a procesadores PowerPC, como el MareNostrum, que

cuenta con 10.240 PowerPC 970MP a 2,3 GHz [4].

Además, todas las videoconsolas dominantes tienen

corazón PowerPC, con el Broadway de Nintendo Wii, Cell

para la PlayStation 3 y Xenon de XBox 360. Y por

supuesto, es una excelente solución para estaciones de

trabajo y equipos de sobremesa, así como portátiles.

En la actualidad, la especificación PowerPC está

gestionada por el consorcio Power.org [5], que incluye

entre sus miembros a IBM y Freescale.

Características Arquitectónicas

Tras conocer los fundamentos de los computadores

RISC, pasaremos a desglosar las particularidades de una

arquitectura que proporciona gran rendimiento

manteniendo la simplicidad de los computadores RISC

originales.

A. Arquitectura del Juego de Instrucciones

La ISA (Instruction Set Architecture) de PowerPC se

describió originalmente en tres libros [6] que contemplaban

las instrucciones de nivel de usuario, el entorno virtual y el

entorno operativo.

El primero describe el uso de los registros e

instrucciones (todas no privilegiadas) típicamente usados

por los programas de aplicación. El segundo describe las

instrucciones que permiten manejar el almacenamiento de

la CPU (cachés, alineamiento de accesos, etc.). Son

instrucciones no privilegiadas, pero que sólo el SO

típicamente usa. El último libro hace referencia a las

instrucciones privilegiadas para el manejo de la traducción

de direcciones, interrupciones, etc.

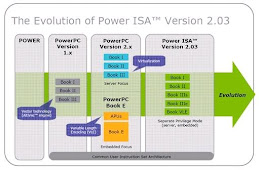

La última versión de la ISA es la 2.03, publicada en

noviembre de 2006, cuenta con los tres libros originales, en

los que se separa el modo privilegiado en las categorías de

servidor y empotrado y un libro adicional de instrucciones

de longitud variable. Incluye soporte para virtualización,

descripción precisa de las extensiones AltiVec para cálculo

vectorial y, lo más importante, fusiona todos los juegos de

instrucciones de PowerPC, POWER y los procesadores

empotrados en un único ISA [7] [8]. Puede observarse en la

la evolución de la ISA Power.

En la especificación básica, las instrucciones tienen un

ancho de codificación fijo de 32 bits. Las instrucciones

aritméticas y lógicas usan un formato de tres operandos,

especificados por el nombre de los registros.

B. Alineamiento de palabras

Originalmente la arquitectura PowerPC se definió para

acceder a memoria usando el alineamiento big-endian (o

del extremo mayor) aunque la mayoría de las

implementaciones de microprocesadores PowerPC tienen la

posibilidad de cambiar en tiempo de ejecución el

alineamiento (endianness) variando un bit del registro MSR

a little-endian (el alineamiento que usa el bus PCI y las

arquitecturas IA-16, IA-32 y AMD64, por ejemplo).

Un ejemplo de CPU que no podía cambiar el endianness

en tiempo de ejecución fue el 970 de IBM, que sólo usa

big-endian.

C. Modos de direccionamiento a memoria

Las CPUs PowerPC direccionan al byte y sólo es posible

el acceso a memoria mediante las instrucciones LOAD y

STORE, que copiarán a los registros del procesador los

valores de la memoria principal o los transferirán a ésta.

Para generar las direcciones se sumará el contenido de

un registro base a un índice proporcionado en la propia

instrucción o en un registro índice. PowerPC permite

actualizar el registro base con la última dirección generada

para, por ejemplo, procesar elementos consecutivos.

D. Conjunto de registros

La arquitectura define 32 registros de propósito general

y otros 32 registros de coma flotante de 64 bits. En función

del modo de operación, los registros de propósito general

tendrán un ancho de 32 ó 64 bits.

Las implementaciones que incorporan el motor vectorial

AltiVec [9] (también llamado VMX por IBM o Velocity

Engine por Apple) incorporan 32 registros adicionales de

128 bits.

E. Motor de cálculo vectorial

Además de los 32 registros vectoriales, los procesadores

PowerPC que implementen el motor AltiVec implementan

instrucciones de control de caché para evitar sobrecargar el

uso de la memoria caché y producir un descenso del

rendimiento.

Como ocurre con las extensiones SSEx de los

procesadores x86, operan en paquetes de datos usando los

registros especiales definidos a tal efecto. La diferencia

radica en que PowerPC define 32 frente a 8 registros de

x86 (AMD64 amplía esta cifra hasta 16) y que ejecuta las

instrucciones vectoriales de forma independiente en un

ciclo y sin requerir un cambio de modo [9], cosa que no se

ha conseguido en los procesadores x86 hasta 2006 con la

introducción de la microarquitectura Core de Intel.

AltiVec fue desarrollado entre 1996 y 1998 y la primera

implementación se produjo en el MPC7400 de Motorola

(G4) que Apple usó para optimizar parte del código de su

nuevo sistema operativo, Mac OS X. Recientemente, se ha

incluido el motor VMX en los procesadores de la línea

POWER de IBM con el futuro POWER6.

Ejemplo de Implementaciones

A continuación se muestran las características de

diversas implementaciones de la arquitectura PowerPC. Se

incluyen los procesadores 601 de IBM y Motorola, 7447 de

Motorola, 970 de IBM y 401, como ejemplo de

microcontrolador.

Además, se incluye una breve revisión al Cell

Broadband Engine (BE) y Xenon y a la nueva apuesta de

IBM, el POWER6.

A. PowerPC 601

El PowerPC 601 es el primer representante de la

arquitectura. Presentado en marzo de 1994, fue

desarrollado por Apple, IBM y Motorola. La necesidad de

sacarlo pronto al mercado hizo que el equipo de desarrollo

de IBM en Austin aceptara una planificación de desarrollo

de tan sólo 12 meses tomando como base de desarrollo la

interfaz de bus del Motorola 88110 [10].

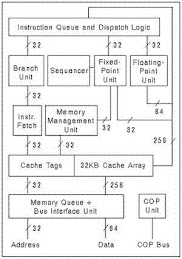

Se trata de un procesador superescalar de 32 bits con

tres unidades de ejecución segmentadas que es capaz de

emitir tres instrucciones de 32 bits por ciclo.

Está implementado en un único chip con 2,8 millones de

transistores, incluyendo los 32 KiB de caché unificada

(asociativa por conjuntos de 8 vías). Se usó la tecnología de

fabricación de 60 micrones (60.000 nm). Existieron

versiones con frecuencias de 50, 66, 80 y 100 MHz.

El pipeline del 601 es relativamente corto (aspecto

característico de los PowerPC hasta la llegada del 970) con

4 etapas para las instrucciones de enteros, 6 para las de

coma flotante y 5 para las LOAD/STORE. Posee 11

unidades funcionales entre las que se

encuentran 2 de coma flotante y una de ejecución de salto

(Branch Unit) con capacidad de ejecución fuera de orden.

Tiene un búfer de instrucciones que le permite tener

hasta 8 instrucciones al vuelo.

B. PowerPC 7447

Tras las implementaciones de la serie 6XX, llegó la serie

7XX, denominada por Apple como G3, que permitió

superar el rendimiento de la serie 6XX, pero que tuvo una

importante carencia: el motor vectorial, que ya tenían sus

competidores x86. El motor vectorial llegaría con el 7400

de Motorola, que sería básicamente un 750 con el añadido

de las extensiones AltiVec.

En 2001 presenta el 7450, que supondría un rediseño

completo de la anterior versión. Con un pipeline un poco

más largo (7 etapas frente a las 4 del 7400) pudo alcanzar

frecuencias mayores, desde los 667 MHz en 2001 a los 2

GHz en la actualidad. La última revisión, el MPC7448 está

fabricada en 90 nm y ofrece cotas de rendimiento por vatio

de entre las mejores del mercado.

El PowerPC 7447 es una pequeña evolución del 7450,

con el comparte filosofía arquitectónica. También tiene un

pipeline de 7 etapas, está fabricado con tecnología de 130

nm e implementado con 58 millones de transistores. Tiene

un caché L1 dividida de 32 KiB de instrucciones y 32 KiB

de datos, una caché L2 interna unificada de 512 KiB y la

versión 7457 tiene una interfaz para caché L3 externa al

chip de la CPU.

Posee tres unidades de enteros simples que manejan más

del 90% de las instrucciones con enteros, además de una

unidad compleja que permite manejar las restantes.

Ofrece 16 registros adicionales de renombrado, ocultos

al programador y compilador que sirven para dar mayor

flexibilidad a la hora de planificar la ejecución de

instrucciones, llegando hasta 16 instrucciones pendientes.

El 7447 implementa las extensiones AltiVec, que

añaden 162 nuevas instrucciones a la ISA Power y tiene 4

unidades de ejecución vectoriales que se pueden observar

en el diagrama de bloques de la figura 6: permutación de

vectores, operaciones de enteros simples, operaciones de

enteros complejos y operaciones de coma flotante, además

de los 32 registros de 128 bits estándar.

La revisión 7447a incluye monitorización de

temperatura y la posibilidad de variar el multiplicador

interno en tiempo de ejecución, característica

especialmente útil en equipos portátiles [11].

C. PowerPC 970

La filosofía de diseño del PowerPC 970 varió respecto a

la del 7450, en este caso se usó un pipeline bastante más

largo, de 14 etapas en el caso de operaciones con enteros,

frente a las 7 del 7450. Esto permite tener hasta 200

instrucciones al vuelo pendientes de confirmar (lo que

incrementa el número de registros de renombrado

necesarios), además de escalar mejor frecuencia. Estas

características, combinadas con un consumo relativamente

reducido (el 970 de 1,8 GHz consume 42 W frente a los 69

del Pentium 4 a 2,8 GHz y los escasos 30 W del 7450 a 1,2

GHz), hicieron que se convirtiera en un chip muy popular.

El PowerPC 970 es un microprocesador superescalar

con modos de operación de 32 y 64 bits que desciende

directamente del POWER4 de IBM e implementa el motor

vectorial VMX (AltiVec).

Comparado con el PowerPC 7450, el 970 tiene un

rendimiento general mayor, pero el tener muchas más

etapas de segmentación hace que cuando es necesario

vaciar el pipeline, la penalización de rendimiento sea

también mayor. Por este motivo, el 970 tiene una caché de

instrucciones el doble de grande que la del 7450 (64 KiB

frente a 32 KiB), además de que ha de incorporar técnicas

avanzadas de predicción de saltos para minimizar los fallos

de pipeline, penalizando el rendimiento [12].

Para mantener el pipeline lleno de instrucciones en todo

momento, se leen de memoria ocho instrucciones por ciclo.

Estas instrucciones se decodifican y dividen en una especie

de micro operaciones llamadas IOPs, que se ejecutarán

fuera de orden.

Pero la mayor mejora de rendimiento del 970 es el bus

frontal que incorpora. Éste está compuesto por dos canales

unidireccionales de 32 bits de ancho que pueden funcionar

hasta a la mitad de la frecuencia de la CPU, es decir, ésta

última tiene un multiplicador de 2x. Los comandos de

control se multiplexan en bus junto con los datos, lo que

hace que se pierda una pequeña cantidad de ancho de banda

(en torno a un 10%), aunque sigue manteniendo una tasa de

transferencia bastante alta (para un FSB de 900 MHz se

llega a los 6,4 GiB/s).

Para concluir, es necesario mencionar que el 970 posee

dos unidades de enteros asimétricas, una unidad de coma

flotante que permite ejecutar operaciones en doble y simple

precisión a la misma velocidad y que tiene 80 registros

disponibles (32 de la ISA PowerPC y 48 de renombrado) y

una implementación total de las extensiones AltiVec, con

unidades de aritmética en coma flotante y entera, lógica y

permuta de vectores [13]. En la figura 8 de aprecian todos

los bloques constitutivos del PowerPC 970.

D. PowerPC 401

El PowerPC 401 es un chip contemporáneo al PowerPC

601, descrito anteriormente. Fue diseñado para entornos

empotrados, como microcontroladores, elementos de redes

(routers, switches…), etc. Para reducir el coste, consumo y

tamaño se eliminaron elementos como la unidad de gestión

de memoria (desparece la paginación) y las unidades de

coma flotante, lo que permitió un consumo de tan sólo 0,1

W en su versión de 100 MHz (1996).

Fue implementado usando únicamente 85.000

transistores. Sólo puede emitir una instrucción por ciclo y

posee un pipeline de tres etapas.

E. Cell Broadband Engine

Este procesador es el resultado de los esfuerzos de Sony,

Toshiba e IBM, que en 2001 comenzaron a desarrollarlo

juntos en lo que se denominó la alianza STI. Entre otros

usos, como televisores de alta definición y servidores blade,

el Cell es el corazón de la nueva Playstation 3 de Sony.

Las primeras versiones del Cell operan a frecuencias de

4,8 GHz (aunque el que lleva la Playstation 3 lo hace a 3,2

GHz y existen prototipos a 65 nm que trabajan a 6 GHz).

A grades rasgos, está formado por un núcleo principal

que implementa toda la ISA Power y ocho elementos

coprocesadores que permiten acelerar de forma paralela

operaciones vectoriales, multimedia y de diversa índole. Al

núcleo principal se le denomina PPE (Power Processing

Element) y a los elementos coprocesadores SPEs

(Synergistic Processing Element) [14].

Tanto el PPE como los SPEs son procesadores RISC. El

PPE implementa la ISA Power de 64 bits, por lo que tiene

los registros marcados por la misma, excepto los registros

del motor VMX, que se incrementan hasta 128. Los SPEs

tienen únicamente 128 registros de 128 bits para almacenar

datos escalares o vectoriales de cualquier tipo.

Aunque el Cell es considerado un chip SMP, realmente

no es así, pues los SPEs no son completamente

independientes ya que necesitan que el PPE les programe

tareas y los sincronice, para lo que se añaden algunas

instrucciones al PPE.

Para comunicar todos los elementos, se implementó el EIB (Element Interconnect Bus), que permite comunicar todos los elementos del chip (12 en total). Se trata de un anillo de 16 bits de ancho por el que los participantes pueden realizar tres transacciones de forma concurrente y que permite más de 200 GiB/s de ancho de banda [15].

Por último, el controlador de memoria XDRAM del Cell permite una tasa de transferencia de más de 25 GiB/s.

F. Xenon

El Xenon es el núcleo de la consola Xbox 360 de Microsoft. Implementa la ISA PowerPC con tres núcleos independientes y simétricos a 3,2 GHz con 32 KiB de caché L1.

Posee 1024 KiB de caché L2 compartida a 1,6 GHz e implementa una derivación de las extensiones VMX, VMX128 (las mismas extensiones VMX, pero con 128 registros y capacidad de multihilo simultáneo).

Proporciona un bus a 5,4 GHz y hasta 21,6 GiB/s de ancho de banda (pico) [16].

G. POWER6

Poco se sabe del nuevo POWER6, salvo que será el sucesor del POWER5+ de IBM.

Se estima que tenga unos 750 millones de transistores (fabricado a 65 nm, aunque con partes a 90 nm) y opere a frecuencias de entre 4 y 6 GHz sin incrementar en gran medida la longitud del pipeline respecto al POWER5+.

Se trata de un procesador dual-core con 128 KiB de caché L1 por core y una caché L2 de 4 MiB compartida. Además, habrá implementaciones con hasta 36 MiB de caché L3 externa [17].

Es el primer procesador de la línea POWER de IBM [3] que incorpora el motor vectorial AltiVec (VMX). Además incluye técnicas de ahorro de energía para su futuro uso en entornos como servidores blade.

CONCLUSIÓN

Como ha podido verse a lo largo de los apartados anteriores, la arquitectura PowerPC nació como alternativa a los procesadores CISC de la época y ha terminado por sustituirlos, pues en la actualidad, éstos poseen un núcleo RISC y un traductor de instrucciones a micro operaciones similares a las RISC.

A lo largo de toda su historia ha ido evolucionando para adecuarse a las necesidades del momento y adaptarse a diferentes escenarios de utilización, de tal forma que se usa en computadores convencionales y empotrados (en los que ha desbancado claramente a la anterior arquitectura dominante, MIPS [18] [19]). Ha evolucionado hasta chips multinúcleo y de bajo consumo y supone una clara alternativa a los procesadores x86 de Intel o AMD.

Además tiene un futuro prometedor, con procesadores como el Cell, que siguen la tendencia actual del paralelismo a nivel de hilo y datos o el POWER6, que además evolucionan técnicas descartadas por otros fabricantes como la supersegmentación y la escalada de frecuencias para incrementar el paralelismo a nivel de instrucción. A lo que hay que añadir el dominio en el mundo del entretenimiento.

Aunque no todo es tan prometedor, pues el principal fabricante de computadores de sobremesa que usaba PowerPC como núcleo de sus equipos, Apple, ha dejado de usarlos, por lo que su expansión es menor y de aquí a unos años se perderá un sistema operativo para PowerPC, quedando, previsiblemente, únicamente Linux como sistema para estas máquinas.

11 comentarios:

Una de las principales ventajas del PowerPC es su capacidad para procesar de forma simultánea múltiples operaciones y permiten un mayor rendimiento informático, característica necesaria en los superordenadores.

El PowerPC ha sido una de las arquitecturas más extendidas gracias a su alto rendimiento y de gran implementación tecnológica, tanto asi que se usa hasta en video juegos, uno de los procesadores PowerPC (Xenon) es el núcleo de la consola Xbox 360 de Microsoft. Esta basado en la ISA PowerPC, cuenta con tres núcleos independientes y simétricos

Listado de procesadores PowerPC

1. 601 MPC601 50 y 66 MHz

2. 602 productos para consumidor (bus de datos y direcciones multiplexados)

3. 603 para ordenadores portátiles

4. 603e

5. 604

6. 604e

7. 620 la primera implementación de 64 bits

8. x704 BiCOMOS implementación PowerPC por Exponential Technologies

9. 750 G3 (1997) 233 MHz y 266 MHz

10. 7400 G4 (1999) 350 MHz

11. 750FX anunciado por IBM en 2001 y disponible en 2002 en 1 GHz.

12. 970 G5 (2003) implementación 64-bit derivada del IBM PowerPC G4 en velocidades de 1,4 GHz, 1,6 GHz, 1,8 GHz, 1,9 GHz, 2,0 GHz, 2,1 GHz, 2,3 GHz, 2,5 GHz, y 2,7 GHz

La arquitectura Power original se basa en varios circuitos, mientras que el PowerPC es una versión reducida de la misma destinada a funcionar en un único circuito. A nivel de procesador puro, el PowerPC demuestra un mejor rendimiento en las operaciones; más allá de eso, la arquitectura PowerPC está preparada directamente para funcionar en sistemas multiprocesador con un máximo de cuatro circuitos cooperando entre sí. PowerPC = rendimiento optimizado del chip mediante tecnología RISC. Yaruby Alcántara.

Como Ya se sabe la tecnologia es muuy cambiante por lo q es de vital importancia estar sobre la marcha. Pero tambien es necesario estar informados de los antecendes de la misma,A lo q cabe destacar en est caso una nota curiosa.

IBM fue la encargada de fabricar el reconocido PowerPC, que en ese tiempo eran unos procesadores no compatibles con la arquitectura x86(Intel y AMD),donde los mismos se encargaban de mover el corazón de los Apple.Hace más de un año esta empresa se cansó de esperar a q IBM modernizase sus procesadores y dio su paso a la Intel,lo q incremento venta en sus equipos.

Pêro ahora la IBM Reaparece y Ahora sin el apoyo de Apple presenta la nueva revisión de su Power PC, el Power 6.donde sus procesadores lograrán velocidades desde 3,5GHz 4,2GHz y 4,7GHz y se han logrado prototipos de hasta 6GHz,cuyo rendimiento promete ser espectacular, de momento se conoce que usan doble núcleo y que el ancho de banda llega a ser de 300GB por segundo.

Nina Villalba E.

No solo se usa el pw pc en la consola del Xbox sino en el nuevo y revolucionario"PS3", donde tendrá un procesador de última generación 3,2Ghz basado en la arquitectura Power PC y fabricado por IBM. Dispondrá de una memoria de 256MB de RAM qué comunicará con la XDR RAM a una velocidad superior a los 50GB por segundo muy superior a la que en estos momentos ofrecen los ordenadores actuales.

ademas de nuevos paquetes denominados"Ubuntu PowerPC",asi q hasta linux se apunta en esto.

En cuanto a la actualidad de los procesadores Power hay que destacar el mas reciente logro de IBM: el Power 595.

El Power595 forma parte de la serie Power6 de microprocesadores destinados a servidores Unix. Se basa en un procesador dual-core a nada menos que 5 GHz, una cifra increíble a la que otras empresas ni siquiera sueñan con alcanzar a medio plazo. El único detalle es que es solo para servidores.

Este procesador en teoría se llevará "por los cachos" a los actuales, coloquialmente hablando; ya que actualemente se manejan chips que oscilan entre los 2 y los 3 GHz, mientras que el Power6 llega a los 5 GHz.

Vale la pena destacar que junto con el lanzamiento del Power595, también se presentó la nueva versión del sustituto de la gama Power570: el Power 575. Este posee la tecnología de refrigeracion por agua llamada "Hydro Cluster".

Ricardo González

Apple ha implantado un nuevo procesador.El PowerPC 603

este es de de más bajo consumo, y con unas características internas a nivel de arquitectura muy similares a las del PowerPC 601.

contando con una velocidad inicial de reloj con la que sale este nuevo procesador es de 75 MHz, en los dos modelos que han aparecido,el Diseño de la caché el diseño externo es de 256 KB ,el Bus del sistema dicha velocidad es de 25 MHz.

Por otra parte, Un aspecto destacable cuando se ve el procesador PowerPC 603 instalado en la placa madre, a diferencia de los modelos equipados con el PowerPC 601, es la carencia de cualquier tipo de radiador para la disipación de calor .

Angel Arismendi

Pros y Contras de las Plataformas:

PC's basadas en PowerPC:

Los PRO:

La nueva arquitectura evita las limitaciones del set de instrucciones x86. Los sistemas corren mucho del Software x86 con la ayuda de emuladores incluidos en los sistemas operativos.

· Los chips son menos caros de fabricar que los procesadores x86 o similares.

· Un altamente exitoso debut en la línea Apple's Power Macintosh a generado interés.

Los Contras:

· La selección de Software nativo es limitada; el Software emulado corre lentamente.

· Los sistemas requieren Windows NT o Unix.

· Los sistemas están disponibles en un número limitado de vendedores y son relativamente caros.

· Bajo volumen significa que los desarrolladores de Software están menos inclinados a optimizar códigos anulando cualquier ventaja del Hardware.

Las PC basadas en Pentium:

Los PRO:

.Estos sistemas corren todos los Software x86 existentes a toda velocidad en los principales sistemas operativos.

· Sus sistemas están disponibles desde cientos de proveedores; la competencia promueve precios bajos.

· Históricamente el aumento de la fabricación a correspondido en forma consistentemente en disminución en el precio.

Los Contra:

· La trayectoria de crecimiento de una arquitectura de 15 años de edad es limitada.

· Estos sistemas no pueden correr el sistema operativo Macintosh.

· El incremento en la variedad de proveedores de sistemas y Software ha afectado a la compatibilidad.

Angel Arismendi

La IBM ofrece herramientas de software y hardware de evaluación que permitan a los procesadores IBM PowerPC y núcleos en las aplicaciones cliente.

Estas soluciones ayudan a acelerar el diseño de los equipos de diseño y los ciclos de actualización, comunicar y gestionar el cambio a través de equipos, software y simplificar el modelado y el seguimiento.

Krlos_8a

Algunas implementaciones del PowerPC...

La implementación mas extendida de este microprocesador, aunque parezca mentira, es en el área automotriz. Según estudios casi la mitad del parque automotor mundial cuenta con al menos un controlador PowerPc.

Por otro lado, otra implementación exitosa del PowerPc es el área de Networking. Como ejemplo, tenemos los módulos para routers de gran escala CISCO Serie 7600 que utilizan seis PowerPC SC8548 a 1.25 GHz (5 de ellos para la clasificación de trafico)...

Ver mas info aqui

Por último, En el 2003 se desarrolló una plataforma para el manejo de aviones de combate F-35 basado en procesadores PowerPC duales.

Publicar un comentario